リスク評価は、設計ライフサイクルで最も重要なステップの 1 つです。そのため、プレシリコン段階から完成品段階に至るまで、設計の各レベルでセキュリティを実装する必要があります。

評価の各段階のセキュリティ

●プレシリコン :チップを製造する必要がないため、評価コストが削減されます。

また、チップの製造を開始する前に信頼性が高まります。

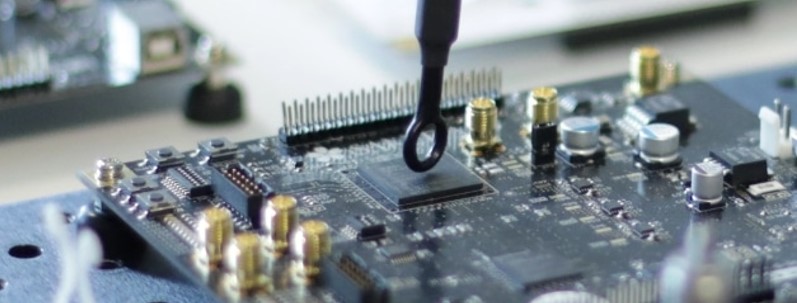

●ポストシリコン:チップをテストしてセキュリティ レベルを確認します。

チップの評価は、設計と製造の重要なステップ

●一部の認証では、事前テストが要求されます。

●評価することで、システムに価値を追加します。

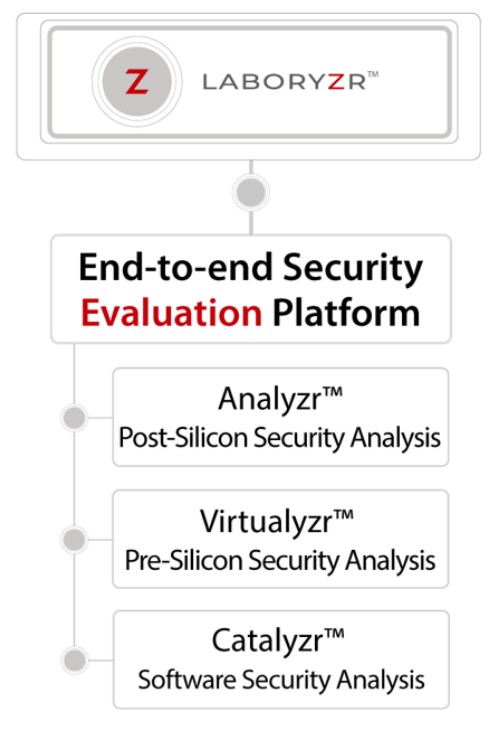

評価の各段階のためのツール

Secure-IC は、Laboryzrと呼ばれる専用のリスク評価およびセキュリティツールにより、プレシリコンから設計プロセス全体を評価できます。製品のライフサイクル全体にわたるリスク評価用に特別に設計された関連ツールセットにより、セキュリティ評価がこれまでになく簡単になりました。

セキュリティ評価ラボ

Laboryzrは、パッシブ/アクティブの分析とその他の分析をカバーします:

●パッシブ :サイドチャネル攻撃の分析

●アクティブ:故障注入攻撃の分析

●ハードウェアトロイの木馬検出

●リバースエンジニアリング防止

Secure-ICは、3つの主要なツールに基づいて、設計ライフサイクルを通じて幅広いセキュリティ評価が実施できます。

| 項目 | 内容 |

|---|---|

| 【Analyzr】 チップ製造後のポストシリコン段階での物理的セキュリティ評価 実際のチップとボードで実施 |

● 潜在的な物理的リークを制御 ● チップのコンプライアンス レベルを確認 ● すぐに使用できる評価ラボ ● サイドチャネル攻撃と故障注入攻撃の測定と分析を実行 ● セキュリティ検証 ● セキュリティの完全性を検証するための攻撃テスト |

| 【Catalyzr】 ソフトウェア評価レポート |

● ソフトウェアセキュリティ検証レイヤー ● 制御フロー、データフロー分析、障害分析 |

| 【Virtualyzr】 チップ製造を開始する前のプレシリコン段階でサイドチャネル セキュリティを評価 |

● IPの最初のソースコードからファウンドリに送られる直前の SoC レイアウトまで、セキュリティを考慮した設計。機能検証ワークフローと連携して実行されるセキュリティ検証レイヤーを提供 ● さまざまな設計レベルでセキュリティチェックポイントを実行可能 ● 設計からセキュリティの脆弱性を検出して特性評価 ● 設計に脆弱性をマッピング ● 測定機器やプラットフォームが不要なため、評価が安価。 ● 混合設計の評価: ハードウェアとソフトウェアの両方 |

Secure-IC は、Common Criteria、FIPS-140、OSCCA などの一般的な認証でお客様が希望する認証レベルに到達できるようサポートするだけでなく、ISO/IEC 17825 や 20085 などのより具体的な標準で目標を達成できるようサポートします。

ICソリューション本部

TEL:045-474-2290